二维半导体可能具有非常有用的应用,特别是作为低功率晶体管的沟道材料。这些材料在极高的厚度下显示出非常高的迁移率,这使得它们成为电子制造中特别有希望的替代硅的替代材料。

尽管具有优势,但迄今为止,在晶体管中实现这些材料已被证明具有挑战性。实际上,二维半导体具有无悬挂键的性质。因此,众所周知,通过原子层沉积(ALD)在材料上沉积超薄的高k栅极电介质(即具有介电特性的物质或绝缘体)非常困难,通常会导致薄膜不连续。

中国南京大学的研究人员最近提出了一种克服这一局限性的新策略,最终可以在2D半导体上沉积栅极电介质。在《自然电子》上发表的一篇论文中,他们报道了使用分子晶体作为籽晶层的二维半导体上高κ栅极电介质的成功ALD。

进行这项研究的研究人员之一王欣然告诉TechXplore:“我们的研究试图解决二维晶体管的高质量栅极电介质集成问题。”“在最先进的Si晶体管中,有效氧化物厚度(EOT)已缩小至小于1 nm。目前,二维材料和Si在EOT,密度方面存在很大差距接口状态(Dit)和栅极泄漏的问题。如果要认真推动2-D晶体管技术,必须克服这一差距。”

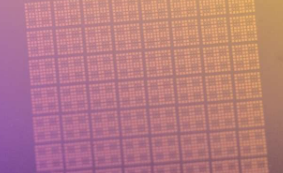

Wang和他的同事介绍的方法可以在石墨烯,二硫化钼(MoS2)和二硒化钨(WSe2)上生产等效氧化物厚度为1 nm的电介质。与使用更常规方法生产的电介质相比,由研究人员的方法产生的电介质具有降低的粗糙度,界面态密度和泄漏。有趣的是,它们还提供了改进的击穿场。

Wang补充说:“除了二维晶体管,我的研究小组探索的另一个方向是有机电子。”“在过去的几年中,我们已经开发出精确控制二维材料表面上分子组装的方法。对于包括PTCDA在内的许多分子,我们证明了我们可以很好地控制生长,因此只有单层(〜0.3 nm) )均匀沉积,界面非常干净。”

Wang和他的研究团队在以前的工作中创建的界面层是目前可获得的最薄的界面层之一。在他们目前的研究中,他们使用这一层来制造工作频率为60 GHz的石墨烯射频晶体管,以及MoS2和WSe2互补金属氧化物半导体晶体管,它们的电源电压为0.8 V,亚阈值摆幅低。 dec-1时为60 mV。最后,他们还使用自己的技术来创建沟道长度为20 nm且开/关比超过107的MoS2晶体管。

Wang说:“我认为我们最有意义的结果是,我们能够在2D材料中实现1 nm EOT。”“人们普遍认为,与大尺寸半导体相比,二维通道可以降低晶体管的功耗。但是,要实现这一点,我们必须使用相同的工作电压,并且可以急剧关闭晶体管(亚阈值摆幅)。接近60 mV / dec)。这两个数量在很大程度上取决于栅极电介质的质量和厚度。我们的研究真正证明了二维半导体在低功耗电子领域的潜力。”

Wang和他的研究小组是第一个成功开发出具有1 nm EOT的2-D晶体管的人,并成功在三种不同的材料上沉积了电介质。引人注目的是,它们所达到的EOT和栅极泄漏与在最新的硅CMOS中观察到的相当,这是该研究领域向前迈出的重要一步。

王说:“我认为仍有很大的改进空间。”“例如,二维晶体管中的Dit仍比Si CMOS高约2个数量级。此外,通过使用更高k的氧化物将EOT进一步降低至约0.8nm将是非常重要的。最后,兼容性我们使用现有的CMOS工艺开发的材料中,仍有待研究。”

教育新闻网

教育新闻网