它被称为CMX940,它针对包括PMR(专用移动无线电),数据调制解调器和海上无线电在内的无线系统。

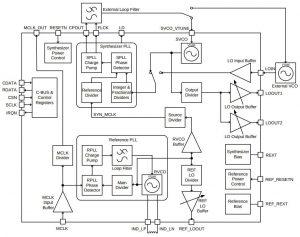

该公司表示:“ CML实现了具有可配置参考路径的双环路架构,该参考路径由单独的PLL和VCO组成,用于最大程度地减小近相噪声并减轻整数和分数边界杂散。”“管理相位噪声和杂散性能对于满足包括ETSI在内的国际标准,对窄带系统强制执行的无线电标准(例如EN 300 113和EN 300 086)至关重要。”

内部VCO工作在2.72 – 4.08GHz,或者外部100MHz – 2GHz VCO。

为了优化每个应用的环路响应,锁相环(PLL)需要外部环路滤波器组件。

PLL参考时钟来自另一个PLL(见图),该PLL将600MHz – 1.2GHz固定频率VCO('RVCO')与片上环路滤波器组件集成在一起,并且仅需一个外部VCO调谐电感器。它需要一个外部10MHz – 40MHz主参考时钟。

CML说:“创新技术已用于提供一种乘以主参考频率的异常低噪声的方法。”“该乘法器与级联的PLL源和参考分频器结合使用时,用户可以选择避免整数边界杂散。”

在500MHz的载波频率下,在12.5kHz偏移下典型的相位噪声为-124dBc / Hz,杂散结果优于-75dBc。

该合成器包括锁定检测,快速锁定功能和自动校准。

有一个可编程的合成器VCO输出分频器和具有线性增益控制的双可变增益输出缓冲器,旨在为系统内的Rx和Tx路径提供本地振荡器频率源。

教育新闻网

教育新闻网